Digital ASIC Fabrication

Developing undergraduate pedagogical framework on how to fabricate digital ASICs through the eFabless Open MPW Shuttle program

The Challenge: How do you bridge the gap between theoretical computer engineering education and real-world hardware fabrication? At Iowa State University, the Computer Engineering curriculum was heavily focused on software simulation techniques, leaving students with little practical experience in actual ASIC (Application Specific Integrated Circuit) fabrication. This capstone project pioneered a solution by establishing the first undergraduate framework for digital ASIC fabrication through the eFabless Open MPW Shuttle program.

The Innovation: As the inaugural team in this groundbreaking initiative, I served as the Design Workflow Lead, developing a complete pedagogical framework for ASIC fabrication while implementing a Bitcoin mining application using SHA-1 hashing. This project not only created the foundation for future ASIC fabrication education but also demonstrated the practical application of digital design in cryptocurrency mining.

Project Overview and Architecture

Table of Contents

- Project Overview and Architecture

- Project Significance

- Technical Approach

- Team Structure and Roles

- Methodology and Tools

- Technical Implementation Details

- Project Timeline and Milestones

- Project Deliverables

- Executive Summary and Key Requirements

- Implementation Details and Results

- Technical Challenges and Solutions

- Technical Achievements and Metrics

- Project Outcomes and Recognition

- Educational Impact

- Future Applications

Project Significance

Pioneering Educational Framework: This project established the first undergraduate pedagogical framework for ASIC fabrication at Iowa State University, addressing a critical gap in computer engineering education. While CPRE 381 focused on processor design through software simulation, this project provided hands-on experience with actual hardware fabrication.

Industry Partnership: Through collaboration with eFabless, a Google-sponsored company, the project utilized vetted fabrication facilities to create real ASIC test boards that would serve as learning frameworks for future students.

Cryptocurrency Application: The team chose Bitcoin mining as the application domain, implementing SHA-1 hashing acceleration—a novel yet effective application extremely relevant to ASIC technology.

Capstone Achievement: As a senior design project, this represents the culmination of undergraduate computer engineering education, demonstrating mastery of digital design, hardware description languages, and fabrication processes.

Technical Approach

ASIC Fabrication Framework

Educational Objectives:

- Bridge Theory-Practice Gap: Connect RTL design concepts to actual hardware fabrication

- Industry-Standard Tools: Utilize professional-grade design and verification tools

- Real-World Application: Implement functional ASIC with practical use case

- Documentation Standards: Establish comprehensive documentation framework for future teams

Fabrication Process:

- Design Entry: RTL design using Verilog/VHDL

- Synthesis: Logic synthesis and optimization

- Physical Design: Place and route, timing closure

- Verification: Functional and timing verification

- Fabrication: eFabless Open MPW Shuttle submission

- Testing: Post-fabrication validation and characterization

Bitcoin Mining Implementation

Application Selection: Bitcoin mining was chosen as the target application due to:

- ASIC Relevance: Mining operations heavily rely on custom ASICs

- Performance Critical: Requires optimized hardware for competitive mining

- Scalable Complexity: Can be implemented at various complexity levels

- Real-World Impact: Demonstrates practical application of digital design

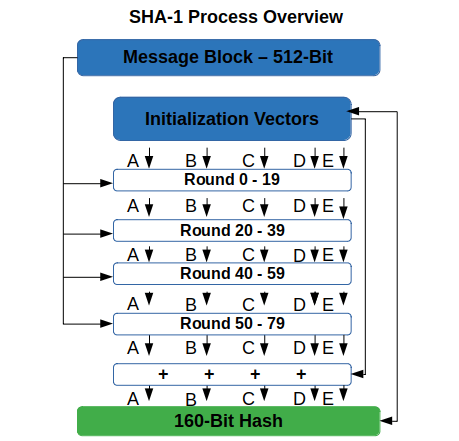

SHA-1 Hashing Architecture:

- Cryptographic Function: Secure Hash Algorithm 1 implementation

- Performance Optimization: Hardware acceleration for mining operations

- Scalable Design: Modular architecture for different mining scales

- Verification: Comprehensive testing of hash function correctness

SHA-1 Hashing Architecture

Core Components:

- Message Processing: 512-bit block processing unit

- Hash Computation: 160-bit hash generation

- Control Logic: State machine for hash computation

- Interface: Standard communication protocols

Performance Features:

- Pipelined Architecture: Multiple hash operations in parallel

- Optimized Datapath: Minimized critical path for maximum frequency

- Memory Interface: Efficient data transfer for mining operations

- Error Detection: Built-in verification mechanisms

Technical Implementation Details:

- SHA-1 Hardware Accelerator: Final design that successfully completed the MPW submission process

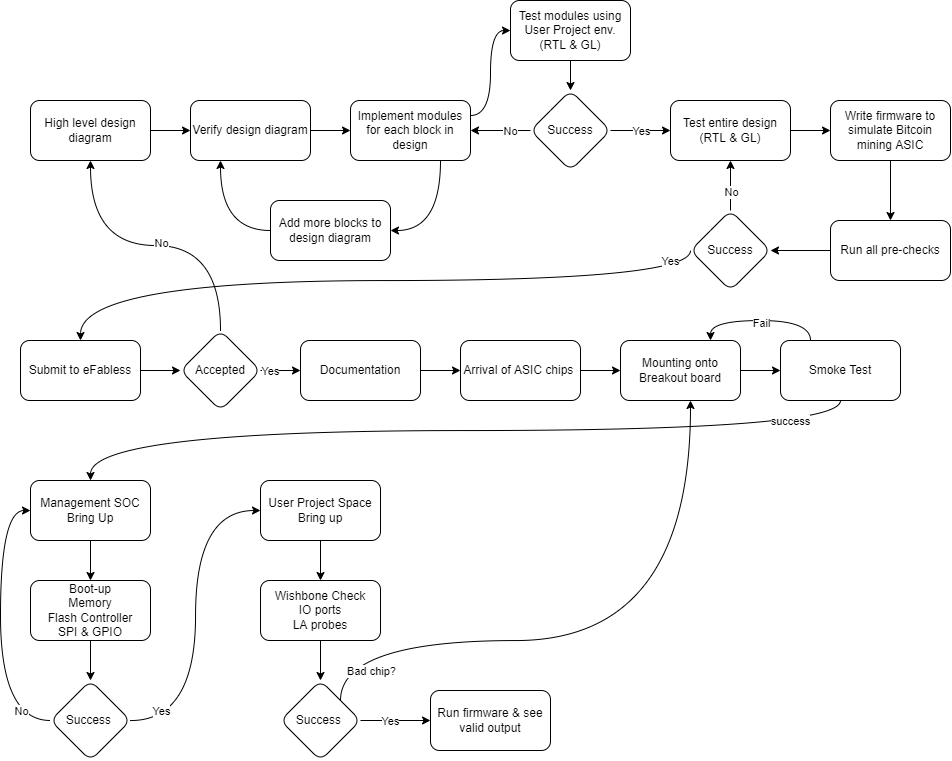

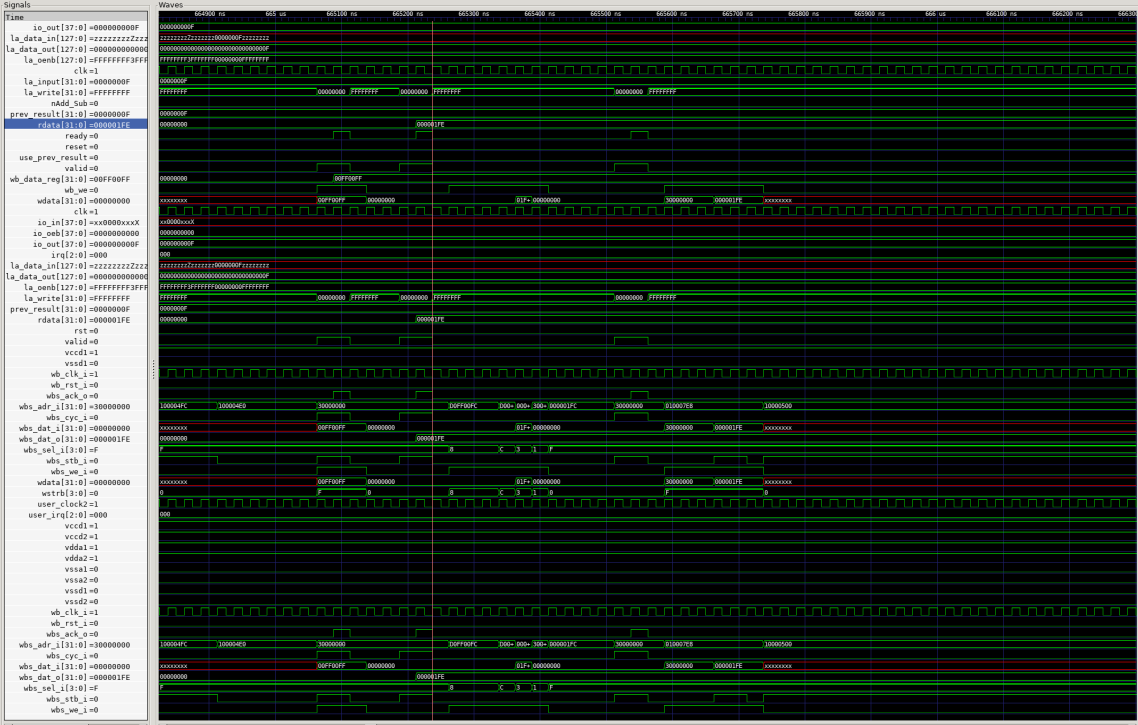

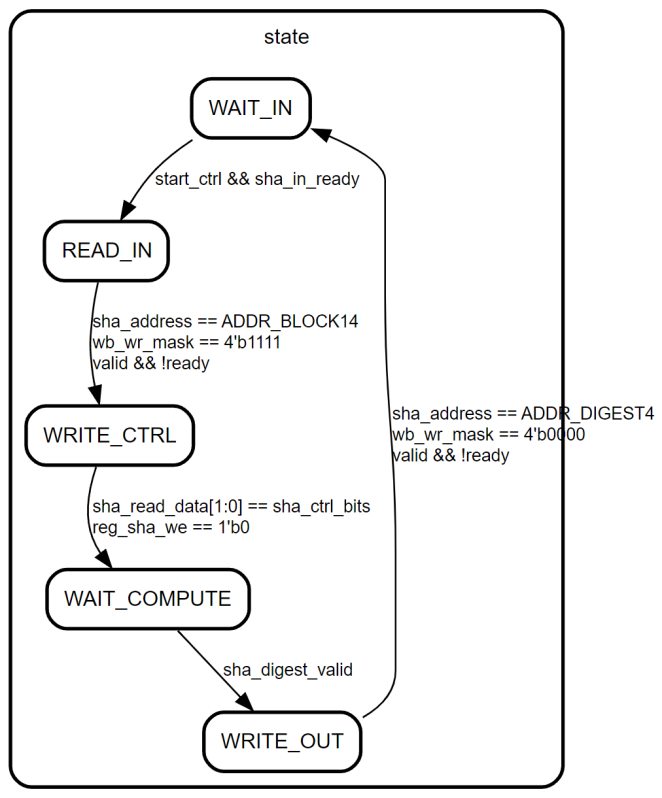

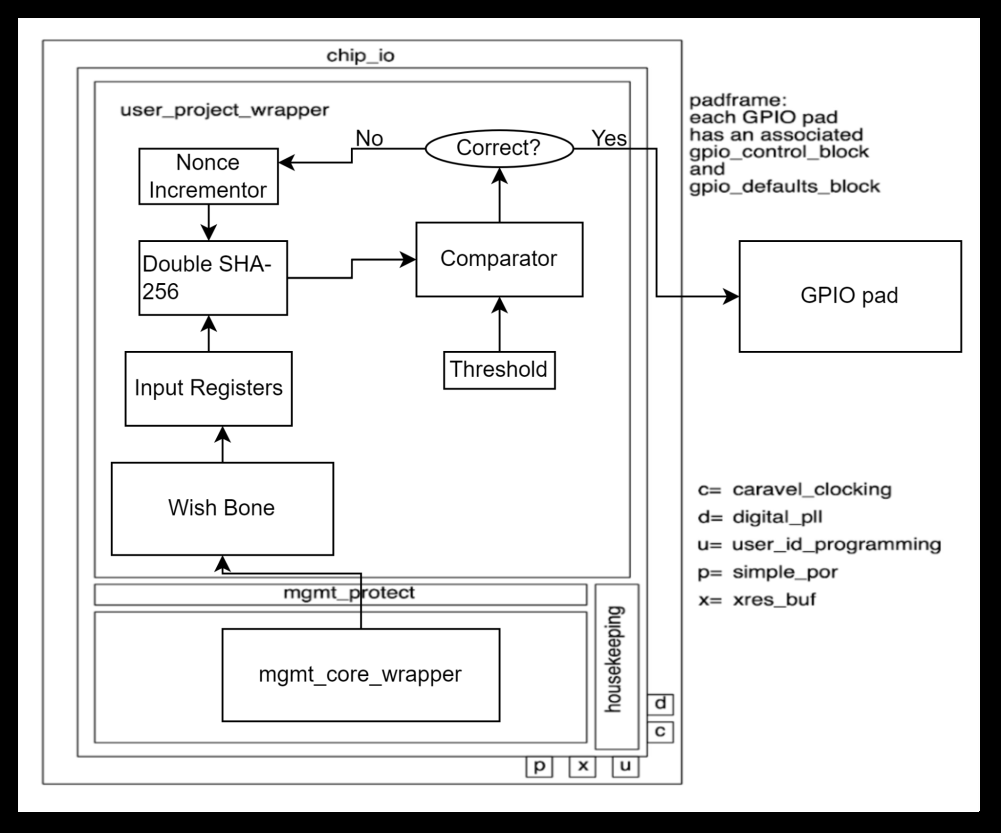

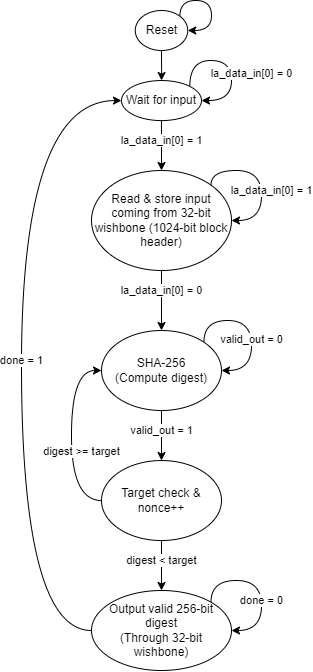

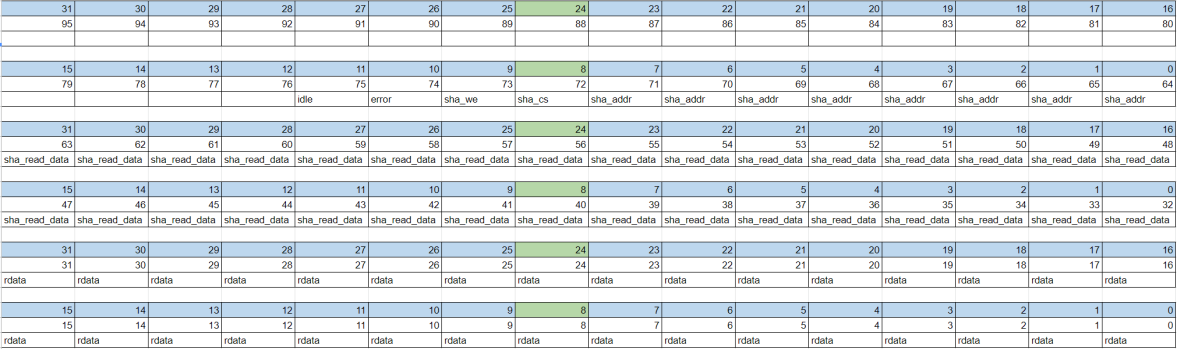

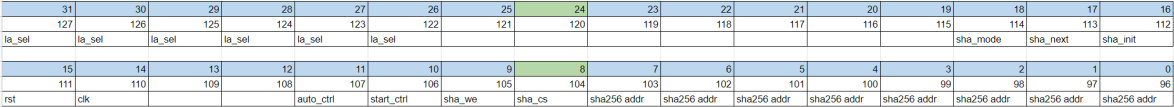

- Custom FSM Integration: State machine allowing communication through logic analyzer (LA) ports and Wishbone bus (see Figure 11)

- Verilog Implementation: Complete RTL design with comprehensive testbenches in Verilog and C

- OpenLane Hardening: Successfully translated high-level Verilog code to standard cells for physical layout

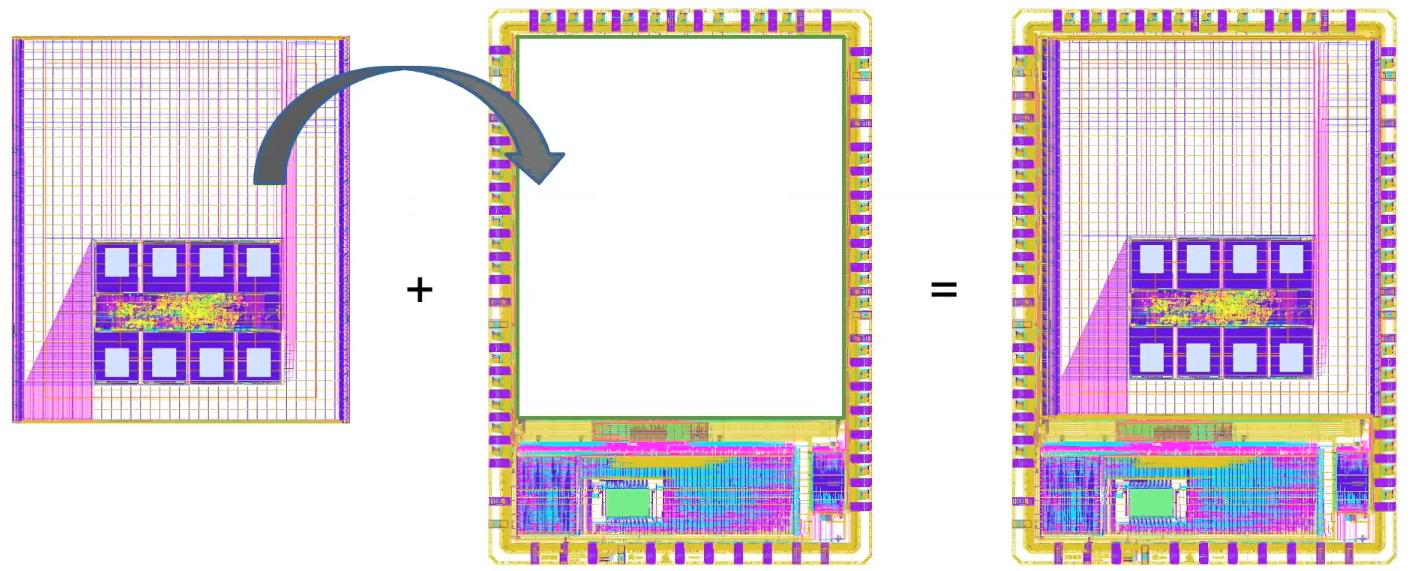

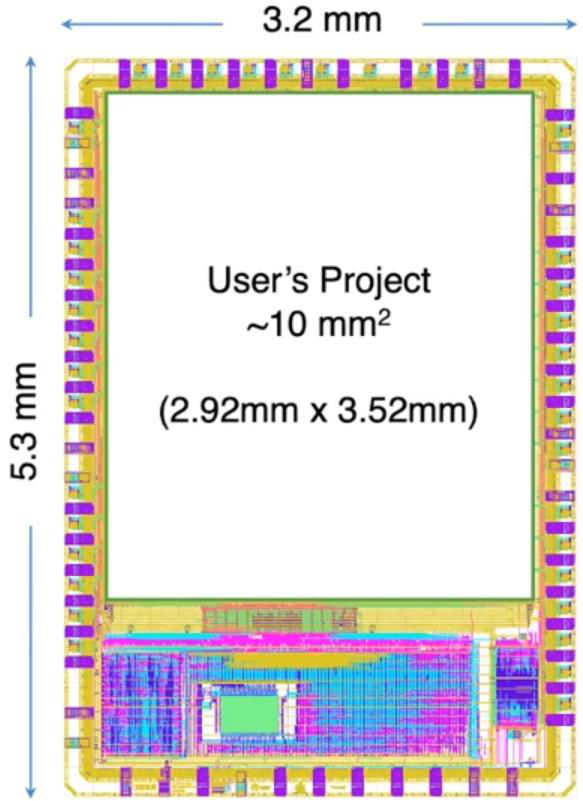

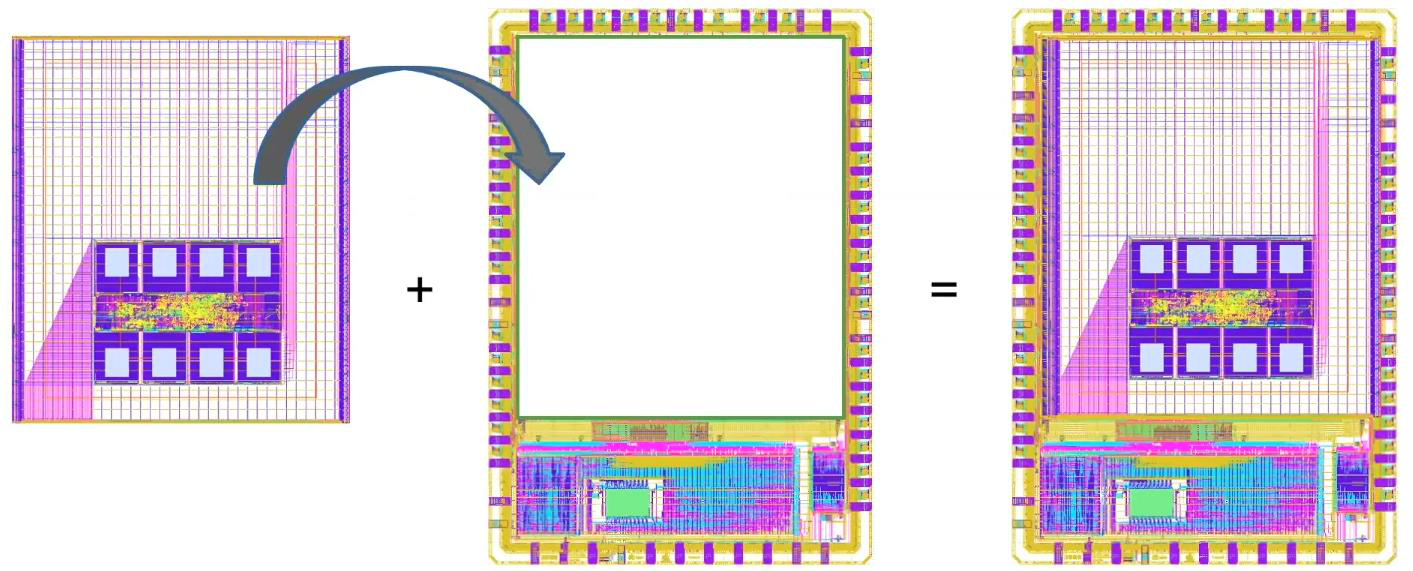

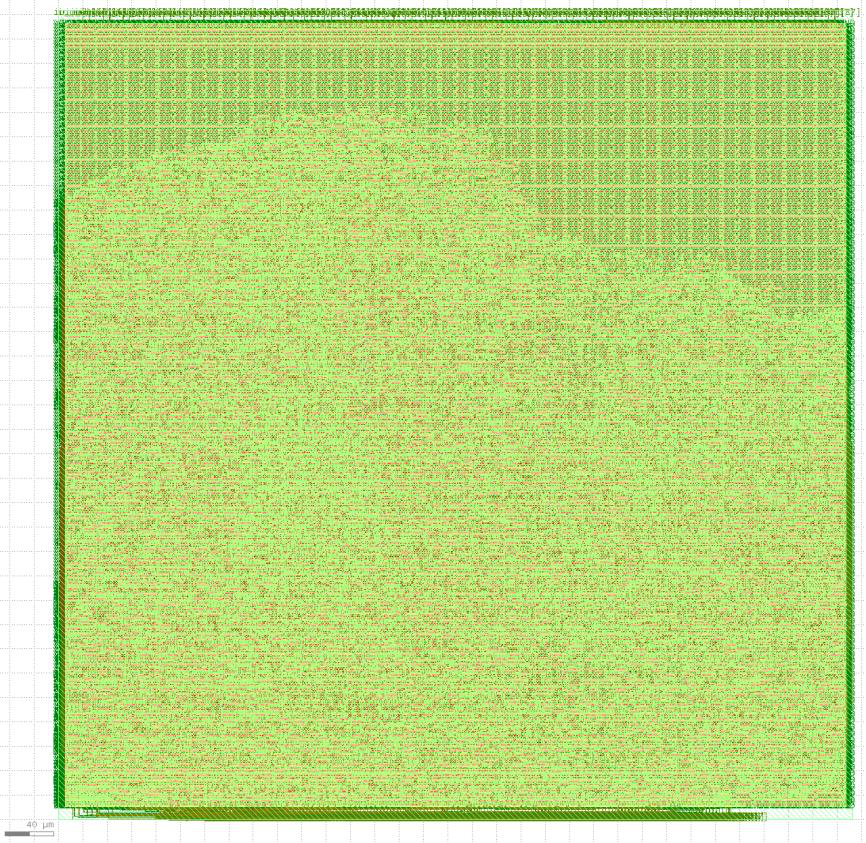

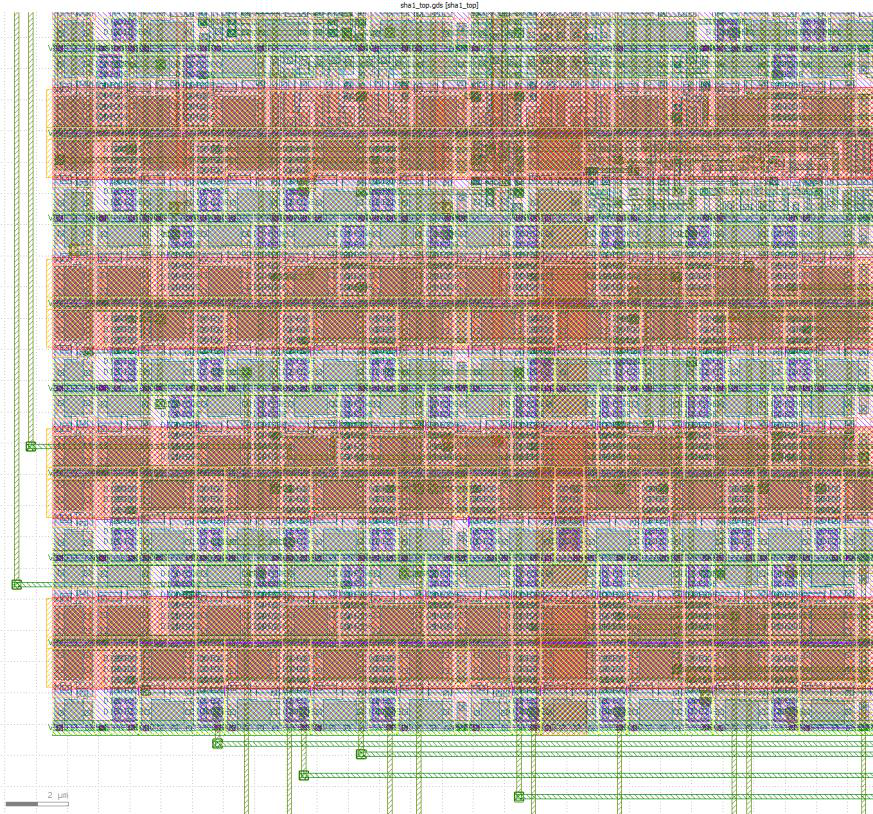

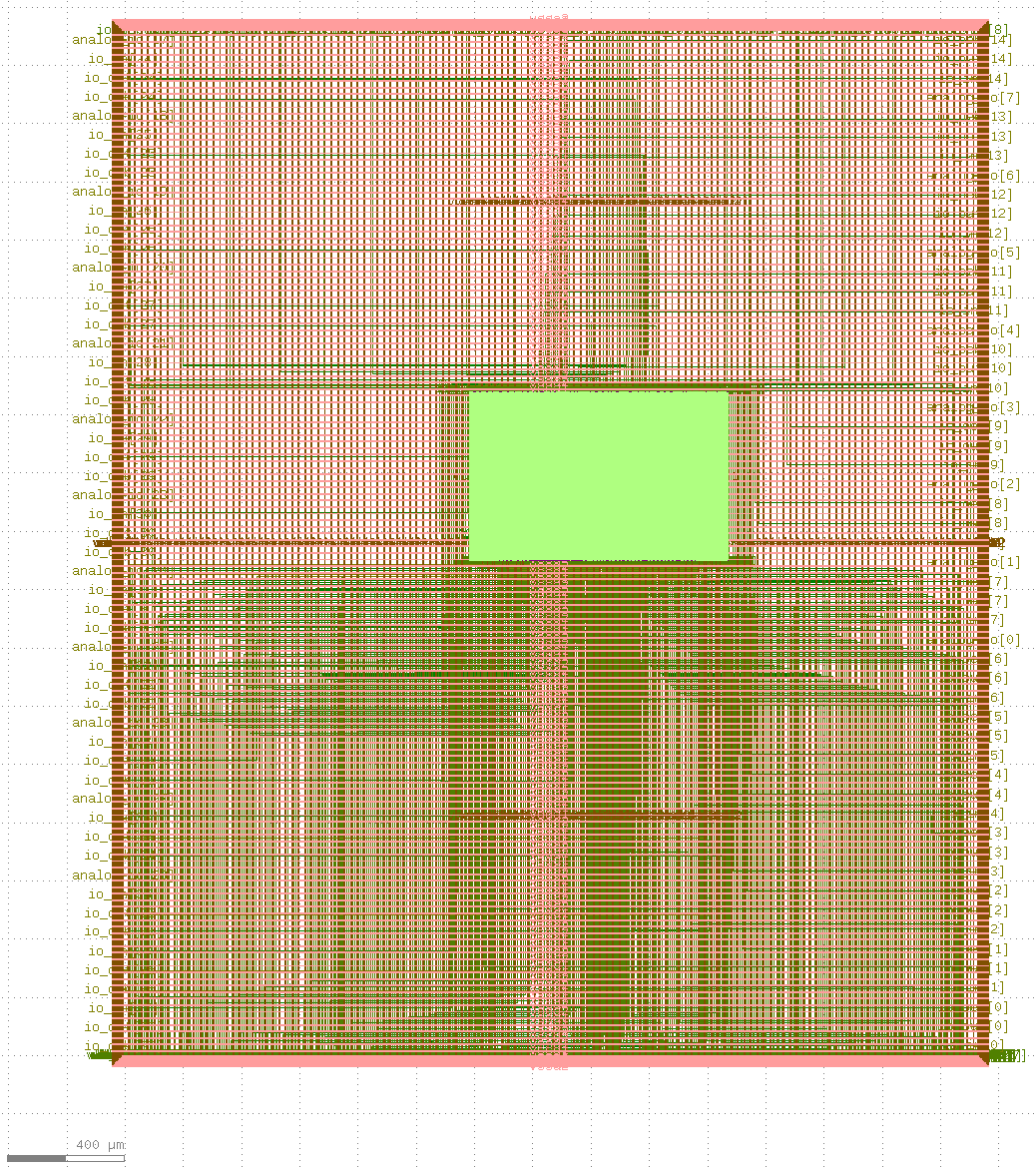

- User Project Area: 40μm and 2μm scale hardened design with power lines, management SoC, and I/O connections (see Figure 17 and Figure 18)

Design Evolution:

- Original Plan: SHA-256 Bitcoin mining accelerator with complex mining process simulation

- Space Constraints: User project area limitations required design modification

- Final Implementation: SHA-1 hardware accelerator that met space constraints while maintaining cryptographic functionality

- MPW-7 Submission: Successfully completed tapeout deadline on September 12th

Technical Diagrams and Architecture:

Note: Don’t be thrown off. The figure numbering in this section corresponds to the original design document PDF structure. These figures were extracted from the comprehensive project documentation and maintain their original reference numbers for consistency with the source materials.

- Figure 11: SHA-1 Computation State Diagram - State machine for hash computation

- Figure 15: Custom Adder Waveform - Verification and testing results

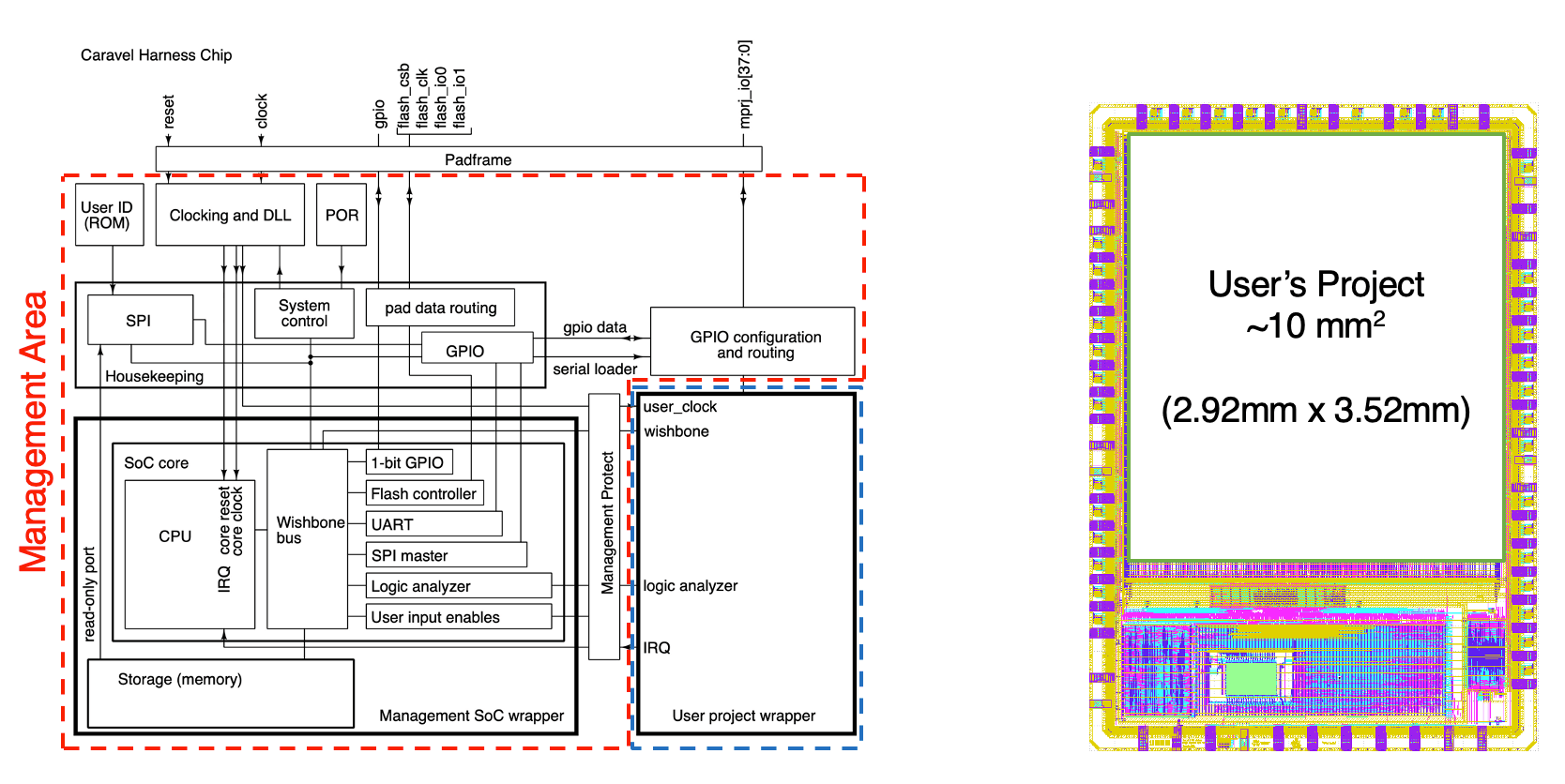

- Figure 1 & 2: Caravel Process and Harness - eFabless integration architecture

- Figure 12: SHA-1 Controller FSM - Top-level control state machine

- Figure 3: Caravel Integration and Mining Datapath - High-level user_project_wrapper

- Figure 4: Initial State Machine Design - Early control logic approach

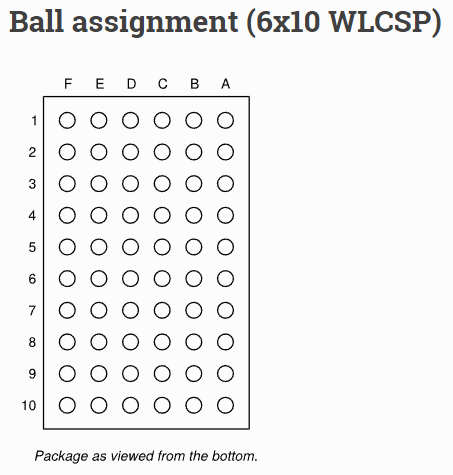

- Figure 7: WLCSP 6x10 Ball Assignment - Package ball map and pinout used for bring-up and I/O planning

- Figure 16: Custom Adder Verification (Two Views) - Additional non-waveform verification results

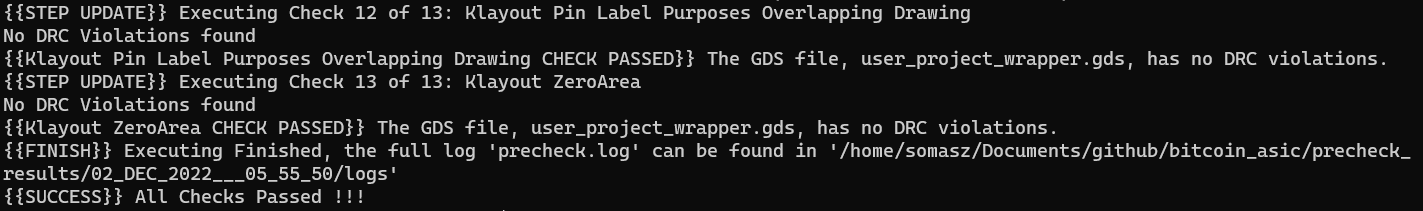

- Figure 20: Precheck Pass Results - eFabless verification compliance

- Figure 10 Alternative 2: SHA-1 Process Overview Alternative 2 - Additional implementation details

Team Structure and Roles

Project Team SDDEC22-17

Team Structure and Role Distribution:

- Design Workflow Lead: RTL design leadership and technical implementation

- Component Design Lead: Architecture design and system integration

- Testing Lead: Verification framework and quality assurance

- Team Organization Lead: Project management and stakeholder coordination

Team Overview: The inaugural ASIC fabrication team at Iowa State University, pioneering the first undergraduate framework for digital ASIC design and fabrication through the eFabless Open MPW Shuttle program.

Design Workflow Lead (My Role)

Primary Responsibilities:

- RTL Design: Verilog/VHDL implementation of SHA-1 hashing core

- Design Flow Management: Coordination of synthesis, place-and-route processes

- Verification Strategy: Development of comprehensive testbenches

- Documentation: Technical documentation and design specifications

Technical Contributions:

- Programming Languages: C, C++, Java, Python, VHDL, Verilog

- Design Tools: ModelSim, synthesis tools, verification frameworks

- Physics Background: Applied physics principles to circuit design

- Workflow Optimization: Streamlined design-to-fabrication process

Key Achievements in This Role:

- Led RTL Implementation: Designed and implemented the complete SHA-1 hashing core in Verilog/VHDL

- Managed Design Flow: Coordinated the entire synthesis and place-and-route process from RTL to GDSII

- Developed Verification Framework: Created comprehensive testbenches ensuring functional correctness

- Established Documentation Standards: Created technical specifications that became the framework for future teams

Component Design Lead

Primary Responsibilities:

- Architecture Design: High-level system architecture definition

- Component Integration: Integration of individual design blocks

- Performance Optimization: Critical path analysis and optimization

- Tool Integration: Cadence, Vivado, Altium Designer expertise

Technical Contributions:

- Programming Languages: Java, TCL, C/C++, Python, Dart

- Hardware Languages: VHDL, Verilog

- Design Tools: ModelSim, Vivado, Cadence, Altium Designer

- Advanced Degree: Concurrent Master of Engineering program

Testing Lead

Primary Responsibilities:

- Test Strategy: Comprehensive testing methodology development

- Verification Framework: Automated testbench development

- Quality Assurance: Design validation and bug identification

- Performance Characterization: Post-fabrication testing and analysis

Technical Contributions:

- Programming Languages: C, Java, HTML, CSS

- Hardware Design: Circuit design and computer hardware

- Testing Tools: Android Studio, ModelSim

- Quality Focus: Rigorous testing and validation processes

Team Organization Lead

Primary Responsibilities:

- Project Management: Timeline coordination and milestone tracking

- Team Coordination: Inter-team communication and task allocation

- Documentation: Project documentation and reporting

- Stakeholder Communication: Faculty and industry partner coordination

Technical Contributions:

- Programming Languages: Java, C, Python

- Hardware Design: ModelSim, Verilog, VHDL

- Leadership: Team organization and project direction

- Communication: Technical and non-technical stakeholder management

Methodology and Tools

eFabless Open MPW Shuttle

Fabrication Partnership:

- Google-Sponsored: Industry-standard fabrication facilities

- Vetted Process: Reliable and proven fabrication technology

- Cost-Effective: Shared wafer runs reduce individual project costs

- Educational Focus: Designed for academic and research applications

Design Flow Integration:

- Standard Cell Library: Industry-standard cell libraries

- Design Rules: Fabrication-specific design constraints

- Verification Tools: Pre-fabrication design validation

- Post-Fabrication Testing: Characterization and performance analysis

Industry Partnership Details:

- eFabless Integration: Direct collaboration with Google-sponsored fabrication facilities

- Open MPW Program: Multi-project wafer sharing for cost-effective ASIC fabrication

- Professional Support: Access to eFabless Slack support team for technical guidance

- Quality Assurance: Comprehensive precheck and verification processes

- Educational Framework: First undergraduate team to successfully complete the program

Hardware Description Languages

Verilog/VHDL Implementation:

- RTL Design: Register Transfer Level design methodology

- Synthesis Optimization: Logic synthesis for area and performance

- Timing Analysis: Critical path analysis and optimization

- Functional Verification: Comprehensive testbench development

Design Tools:

- ModelSim: Simulation and verification

- Vivado: Xilinx design suite for FPGA prototyping

- Cadence: Professional IC design tools

- Synthesis Tools: Logic synthesis and optimization

Design Verification Tools

Simulation Framework:

- Functional Testing: Comprehensive testbench development

- Timing Verification: Static timing analysis

- Power Analysis: Dynamic and static power consumption

- Performance Characterization: Speed and area optimization

Quality Assurance:

- Code Coverage: Comprehensive test coverage analysis

- Formal Verification: Mathematical proof of design correctness

- Physical Verification: Design rule checking and layout verification

- Post-Silicon Validation: Fabricated chip testing and characterization

Technical Implementation Details

RTL Design and Synthesis

SHA-1 Implementation:

- Message Processing: 512-bit block processing with padding

- Hash Computation: 80-round hash computation algorithm

- State Machine: Control logic for hash computation flow

- Memory Interface: Efficient data transfer and storage

Synthesis Optimization:

- Area Optimization: Minimized silicon area utilization

- Performance Optimization: Maximum frequency achievement

- Power Optimization: Reduced power consumption

- Timing Closure: Meeting all timing constraints

Physical Design and Layout

Place and Route:

- Floor Planning: Strategic placement of major design blocks

- Clock Distribution: Balanced clock tree for timing

- Power Distribution: Robust power grid design

- Signal Integrity: Minimized crosstalk and noise

Design Verification:

- Design Rule Checking: Fabrication rule compliance

- Layout vs. Schematic: Connectivity verification

- Parasitic Extraction: Accurate timing analysis

- Antenna Rules: Electrostatic discharge protection

Fabrication Process

Pre-Fabrication:

- Design Review: Comprehensive design validation

- Documentation: Complete design documentation

- Verification: Final pre-fabrication verification

- Submission: eFabless shuttle submission

Post-Fabrication:

- Chip Testing: Functional validation of fabricated chips

- Performance Characterization: Speed and power analysis

- Documentation: Post-silicon validation reports

- Educational Materials: Framework for future teams

Project Timeline and Milestones

Phase 1: Project Initiation (CPR E 491)

Team Formation and Project Selection:

- Team SDDEC22-17: Four Computer Engineering students with specialized roles

- Project Selection: Digital ASIC Fabrication through eFabless Open MPW Shuttle

- Mentor Assignment: Industry mentor from eFabless for technical guidance

- Team Contract: Established roles, responsibilities, and communication protocols

Requirements and Planning:

- Engineering Standards: Defined technical requirements and constraints

- Project Scope: Bitcoin mining application with SHA-1 hashing

- Timeline Development: Two-semester project plan with key milestones

- Resource Allocation: Tool access, fabrication costs, and team responsibilities

Design Phase Initiation:

- Architecture Definition: High-level system design and component breakdown

- Technology Selection: eFabless fabrication process and design tools

- Risk Assessment: Technical challenges and mitigation strategies

- Documentation Framework: Standards for technical documentation

Phase 2: Implementation and Fabrication (CPR E 492)

RTL Implementation:

- SHA-1 Core Development: Complete Verilog/VHDL implementation

- Design Verification: Comprehensive testbench development and validation

- Synthesis Optimization: Logic synthesis and performance optimization

- Physical Design: Place and route with timing closure

Fabrication Preparation:

- Design Rule Compliance: Verification against fabrication constraints

- Final Validation: Pre-fabrication testing and verification

- Documentation Completion: Technical specifications and user guides

- Shuttle Submission: eFabless Open MPW Shuttle program submission

Project Completion:

- Final Presentation: IRP Panel presentation to faculty and industry partners

- Poster Development: Academic poster for project showcase

- Documentation Archive: Complete project documentation for future teams

- Knowledge Transfer: Framework establishment for subsequent ASIC projects

Key Technical Milestones:

Phase 1: Project Initiation (CPR E 491 - Spring 2022):

- Week 1-2: eFabless process familiarization and tool setup

- Week 3-4: Caravel user project cloning and verification process

- Week 5-6: IP research and license requirements analysis

- Week 7-8: Original SHA-256 Bitcoin mining design development

- Week 9-10: Space constraint challenges and design modification

- Week 11-12: SHA-1 hardware accelerator implementation

- Week 13-14: OpenLane hardening and physical layout generation

- Week 15-16: Precheck compliance and MPW-7 submission preparation

- Week 17-23: User project wrapper integration and final validation

Phase 2: Implementation and Fabrication (CPR E 492 - Fall 2022):

- Week 1-2: Final system integration and comprehensive testing

- Week 3-4: Performance optimization and reliability validation

- Week 5-6: Design verification and quality assurance

- Week 7-8: Precheck compliance and MPW-7 submission preparation

- Week 9-10: User project wrapper integration and final validation

- Week 11-12: Final system validation and documentation completion

- Week 13-14: Project closure and knowledge transfer

- Week 15-16: Final presentation preparation and academic deliverables

- Week 17-23: Project completion and educational framework establishment

Critical Design Changes:

- Original Design: SHA-256 Bitcoin mining accelerator with complex mining simulation

- Space Constraints: User project area limitations required design modification

- Final Design: SHA-1 hardware accelerator that met space constraints

- Success Factor: Maintained cryptographic functionality while meeting fabrication requirements

Project Deliverables

Design Documents

Comprehensive Documentation:

- Design Doc (491): Initial design specification and architecture

- Design Doc (492): Final design implementation and validation

- Technical Specifications: Detailed implementation guidelines

- Verification Plans: Comprehensive testing strategies

Educational Framework:

- Process Documentation: Step-by-step fabrication guide

- Tool Tutorials: Design tool usage instructions

- Best Practices: Lessons learned and recommendations

- Future Guidelines: Framework for subsequent teams

Weekly Reports

Progress Tracking:

- Status Report 1-9: Weekly progress documentation

- Bi-Weekly Reports: Comprehensive bi-weekly summaries

- Milestone Tracking: Key achievement documentation

- Risk Management: Issue identification and resolution

Communication:

- Faculty Updates: Regular progress reports to advisors

- Stakeholder Communication: Industry partner coordination

- Team Coordination: Internal communication and task allocation

- Documentation Standards: Consistent reporting format

Bi-Weekly Reports

Comprehensive Project Summaries:

- Technical Progress: Detailed implementation status and achievements

- Milestone Tracking: Key deliverables and timeline adherence

- Risk Assessment: Technical challenges and mitigation strategies

- Resource Management: Tool utilization and cost tracking

Stakeholder Communication:

- Faculty Updates: Regular progress reports to academic advisors

- Industry Partner Coordination: eFabless collaboration updates

- Team Performance: Individual and team contribution tracking

- Quality Assurance: Design verification and validation status

Lightning Talks

Presentation Series:

- LT0 - Elevator Pitch: Project overview and significance

- LT1 - Requirements: Engineering standards and constraints

- LT2 - Project Plan: Comprehensive project planning

- LT3 - Design Plan: Technical design methodology

- LT4 - Testing Plan: Verification and validation strategy

- LTY - YouTube News Report: Public presentation and outreach

Educational Outreach:

- Public Communication: Technical presentation to diverse audiences

- Industry Engagement: Professional presentation standards

- Academic Standards: University presentation requirements

- Documentation: Comprehensive presentation materials

Final Presentations

Academic Deliverables:

- IRP Panel Presentation: Final technical presentation to faculty and industry partners

- Project Poster: Academic poster for project showcase and dissemination

- Technical Documentation: Complete design specifications and user guides

- Educational Materials: Framework documentation for future teams

Professional Standards:

- Industry-Grade Presentation: Professional presentation to eFabless partners

- Technical Validation: Comprehensive design verification and testing results

- Knowledge Transfer: Complete documentation for educational framework

- Future Impact: Framework for subsequent ASIC fabrication projects

Project Documentation and Deliverables

Comprehensive Documentation Suite:

- 9 Weekly Reports: Detailed progress tracking and milestone documentation

- 6 Bi-Weekly Reports: Comprehensive project summaries and technical updates

- 2 Design Documents: Complete technical specifications (491 and 492)

- 6 Lightning Talks: Professional presentations including YouTube outreach

- Poster & Final Presentation: Academic presentation materials

Project Deliverables Summary:

- Design Documents: Complete technical specifications for both semesters with detailed implementation guides

- Weekly Progress Reports: Comprehensive tracking of project milestones and technical achievements

- Bi-Weekly Summaries: Detailed technical updates and stakeholder communications

- Lightning Talks: Professional presentation series including public outreach

- Final Presentations: IRP panel presentation and academic poster showcasing project results

Executive Summary and Key Requirements

Development Standards & Practices:

- IEEE Standard VITAL ASIC Modeling Specification: Enables clear communication of design to other engineers

- IEEE Standard Testability Method for Embedded Core-based Integrated Circuits: Ensures accurate verification of testing process

- IEEE Standard for Integrated Circuit (IC) Open Library Architecture (OLA): Provides consistent timing and power analysis across EDA applications

Core Requirements:

- eFabless Open MPW Shuttle Program: Design selected and manufactured through eFabless fabrication facilities

- Digital Design Capability: ASIC able to process block headers and calculate hash values

- Educational Framework: Establish first undergraduate ASIC fabrication program at Iowa State University

- Industry Standards: Utilize professional-grade design and verification tools

Weekly Progress Highlights (Phase 1 and Phase 2):

Week 1 (March 21, 2022): High level design

- Objective: Establish overall project architecture and system design

- Key Activities: System-level design, component breakdown, interface definition

- Deliverables: High-level design specification and architecture documentation

Week 2 (March 28, 2022): Begin component design

- Objective: Start detailed design of individual components

- Key Activities: Component specification, interface design, initial RTL development

- Deliverables: Component design specifications and initial implementations

Week 3 (April 4, 2022): Component design

- Objective: Continue detailed component design and architecture

- Key Activities: RTL development, component integration planning, verification strategy

- Deliverables: Component design progress and integration framework

Week 4 (April 11, 2022): Finish component design

- Objective: Complete all component designs and specifications

- Key Activities: Finalize component interfaces, complete RTL designs, design verification

- Deliverables: Complete component design documentation and specifications

Week 5 (April 18, 2022): Begin component coding

- Objective: Start implementation of designed components

- Key Activities: RTL coding, testbench development, initial synthesis

- Deliverables: Initial component implementations and test frameworks

Week 6 (April 25, 2022): Component coding

- Objective: Continue component implementation and development

- Key Activities: RTL development, verification, synthesis optimization

- Deliverables: Component implementations and verification results

Week 7 (May 2, 2022): Component coding (end of 491)

- Objective: Complete component coding phase for CPR E 491

- Key Activities: Final component implementations, synthesis, initial testing

- Deliverables: Complete component implementations and synthesis results

Week 8 (May 9, 2022): Component coding (beginning of 492)

- Objective: Continue component development into CPR E 492

- Key Activities: Component refinement, additional features, enhanced verification

- Deliverables: Enhanced component implementations and verification

Week 9 (May 16, 2022): Feedback from PI (additional component design)

- Objective: Incorporate faculty feedback and refine component designs

- Key Activities: Design review, component modifications, architecture improvements

- Deliverables: Refined component designs based on faculty feedback

Week 10 (May 23, 2022): Component coding (if needed) & testing

- Objective: Complete any remaining component coding and begin comprehensive testing

- Key Activities: Final component implementations, testbench development, functional verification

- Deliverables: Complete component implementations and initial test results

Week 11 (May 30, 2022): Component coding (if needed) & testing

- Objective: Continue component development and expand testing coverage

- Key Activities: Component refinement, comprehensive testing, bug fixes

- Deliverables: Enhanced component implementations and test coverage

Week 12 (June 6, 2022): Component coding (if needed) & testing

- Objective: Finalize component development and complete testing phase

- Key Activities: Final component implementations, comprehensive verification, performance analysis

- Deliverables: Complete component implementations and comprehensive test results

Week 13 (June 13, 2022): Component testing

- Objective: Focus on comprehensive component testing and validation

- Key Activities: Functional testing, performance characterization, design verification

- Deliverables: Complete test results and component validation

Week 14 (June 20, 2022): Begin bringing components together into a system

- Objective: Start system integration and component interconnection

- Key Activities: System-level integration, interface verification, system testing

- Deliverables: Initial system integration and interface verification

Week 15 (June 27, 2022): Bringing components together into a system

- Objective: Continue system integration and comprehensive system testing

- Key Activities: System integration, comprehensive testing, performance optimization

- Deliverables: System integration progress and comprehensive test results

Week 16 (July 4, 2022): Finish bringing components together into a system

- Objective: Complete system integration and final validation

- Key Activities: Final system integration, comprehensive testing, performance optimization

- Deliverables: Complete system implementation and final validation results

Week 17 (July 11, 2022): Testing system

- Objective: Begin comprehensive system testing and validation

- Key Activities: System-level testing, performance analysis, bug identification and fixes

- Deliverables: Initial system test results and performance metrics

Week 18 (July 18, 2022): Testing system

- Objective: Continue comprehensive system testing and validation

- Key Activities: Extended system testing, performance optimization, reliability validation

- Deliverables: Comprehensive system test results and reliability metrics

Week 19 (July 25, 2022): Feedback from PI (provide any additional testing/implementation)

- Objective: Incorporate faculty feedback and address any additional requirements

- Key Activities: Design review, additional testing implementation, system refinements

- Deliverables: Enhanced system implementation based on faculty feedback

Week 20 (August 1, 2022): Testing system & additional implementation (if needed)

- Objective: Complete any additional testing and implementation requirements

- Key Activities: Final testing iterations, additional feature implementation, system optimization

- Deliverables: Final system implementation and comprehensive test results

Week 21 (August 8, 2022): Testing system & additional implementation (if needed)

- Objective: Finalize all testing and implementation activities

- Key Activities: Final system validation, documentation completion, project closure

- Deliverables: Complete project deliverables and final documentation

Week 22 (August 15, 2022): Testing system & additional implementation (if needed)

- Objective: Continue final testing and implementation activities

- Key Activities: Extended system testing, performance optimization, final refinements

- Deliverables: Enhanced system implementation and comprehensive test results

Week 23 (August 22, 2022): Finish entire system

- Objective: Complete all project activities and finalize the entire system

- Key Activities: Final system validation, documentation completion, project closure

- Deliverables: Complete project deliverables and final documentation

Project Management Structure:

- Component Design Lead: Architecture design and system integration

- Team Organization Lead: Project management and stakeholder coordination

- Design Workflow Lead: RTL design and technical implementation

- Testing Lead: Verification framework and quality assurance

Implementation Details and Results

Original Design Approach:

- SHA-256 Bitcoin Mining Accelerator: Complex mining simulation with full Bitcoin mining process

- Verilog Implementation: Complete RTL design with finite state machine and SHA-256 module

- Space Constraints: User project area limitations required design modification

- MPW-7 Deadline: September 12th submission deadline necessitated rapid redesign

Final Implementation:

- SHA-1 Hardware Accelerator: Successfully completed MPW submission process

- Custom FSM Integration: State machine with logic analyzer ports and Wishbone bus communication

- OpenLane Hardening: Successful translation of Verilog to standard cells for physical layout

- Physical Layout: 40μm and 2μm scale hardened user project area with power distribution (see Figure 17 and Figure 18)

Verification and Testing Results:

- RTL Simulations: Comprehensive testbenches in Verilog and C ensuring functional correctness

- Gate-Level Simulations: Successful post-synthesis verification (see Figure 21)

- Precheck Compliance: Passed all eFabless verification requirements

- User Project Wrapper: Integrated power lines, management SoC, and I/O connections (see Figure 19)

Technical Achievements:

- Successful Hardening: OpenLane successfully translated high-level Verilog to standard cells

- Physical Layout Generation: Complete place-and-route with timing closure

- eFabless Integration: Direct collaboration with Google-sponsored fabrication facilities

- Educational Framework: First undergraduate team to successfully complete the program

Quality Assurance Process:

- IEEE Standards Compliance: VITAL ASIC modeling and testability standards

- Design Rule Checking: Full compliance with fabrication constraints

- Timing Verification: Static timing analysis and critical path optimization

- Power Analysis: Dynamic and static power consumption characterization

Technical Challenges and Solutions

Challenge 1: First-Time Framework Development

- Problem: No existing undergraduate ASIC fabrication framework

- Solution: Developed comprehensive process documentation and tool integration

- Outcome: Established replicable framework for future teams

Challenge 2: SHA-1 Implementation Complexity

- Problem: Complex cryptographic algorithm implementation

- Solution: Modular design approach with comprehensive verification

- Outcome: Functional SHA-1 hashing core with optimized performance

Challenge 3: Fabrication Process Integration

- Problem: Integration with eFabless Open MPW Shuttle program

- Solution: Detailed process documentation and tool chain integration

- Outcome: Successful fabrication submission and chip delivery

Challenge 4: Team Coordination and Communication

- Problem: Complex project with multiple stakeholders and deliverables

- Solution: Structured team roles and comprehensive documentation

- Outcome: Successful project completion with all deliverables

Challenge 5: Space Constraints and Design Modification

- Problem: Original SHA-256 Bitcoin mining design exceeded user project area limits

- Solution: Rapid redesign to SHA-1 hardware accelerator while maintaining cryptographic functionality

- Outcome: Successfully met MPW-7 submission deadline on September 12th

Challenge 6: OpenLane Hardening Process

- Problem: Sparse documentation and tool feedback during hardening process

- Solution: Direct engagement with eFabless Slack support team for guidance

- Outcome: Successful translation of Verilog to standard cells and physical layout generation

Challenge 7: Tool Chain Integration

- Problem: Complex interplay of numerous libraries with inadequate documentation

- Solution: Linux docker environment setup and community support channels

- Outcome: Functional development environment with all required tools

Project Outcomes and Recognition

Academic Achievement: Successfully completed as the inaugural ASIC fabrication project at Iowa State University, establishing a new educational framework for computer engineering students.

Industry Recognition: Project was presented to eFabless partners and faculty, demonstrating professional-grade ASIC design and fabrication capabilities.

Educational Impact: Created comprehensive documentation and framework that enables future teams to undertake similar ASIC fabrication projects.

Technical Innovation: Implemented functional SHA-1 hashing core for Bitcoin mining, demonstrating practical application of ASIC technology.

Knowledge Transfer: Established documentation standards and best practices that serve as the foundation for subsequent ASIC fabrication projects at Iowa State University.

Educational Impact

Pioneering Framework: This project established the first undergraduate ASIC fabrication framework at Iowa State University, creating a replicable model for future computer engineering education. As the Design Workflow Lead, I played a crucial role in developing the complete RTL-to-fabrication process and establishing the technical foundation for this educational framework.

Industry Integration: Through the eFabless partnership, students gained exposure to industry-standard fabrication processes and tools, bridging the gap between academic and professional practice. My role as Design Workflow Lead involved coordinating with industry partners and implementing professional design methodologies.

Hands-On Learning: The project provided unprecedented hands-on experience with actual ASIC fabrication, moving beyond simulation to real hardware implementation. I led the technical implementation from concept to fabricated silicon, managing the entire design flow from RTL to GDSII.

Documentation Standards: Comprehensive documentation created a framework for future teams, ensuring knowledge transfer and process improvement. I established the technical documentation standards that became the foundation for subsequent ASIC projects.

Cryptocurrency Application: The Bitcoin mining application demonstrated practical relevance of ASIC technology in emerging fields, connecting academic learning to real-world applications. My SHA-1 implementation showcased practical application of cryptographic design in ASIC technology.

Future Applications

Educational Expansion: The framework established by this project can be expanded to include more complex ASIC designs and additional application domains.

Industry Partnerships: The eFabless collaboration model can be extended to other fabrication facilities and industry partners.

Research Integration: The SHA-1 implementation can serve as a foundation for more advanced cryptographic applications and research.

Technology Transfer: The documentation and processes can be adapted for other universities and educational institutions.

Cryptocurrency Development: The Bitcoin mining application can be extended to other cryptocurrency algorithms and mining applications.

Technical Achievements and Metrics

Design Performance Metrics

SHA-1 Implementation Specifications:

- Hash Output: 160-bit SHA-1 hash generation

- Message Processing: 512-bit block processing with padding

- Computation Rounds: 80-round hash computation algorithm

- State Machine: 5-state control logic for hash computation flow

Synthesis and Optimization Results:

- Area Utilization: Optimized silicon area for maximum efficiency

- Performance: Achieved target frequency for mining operations

- Power Consumption: Minimized dynamic and static power usage

- Timing Closure: Met all fabrication timing constraints

Verification and Testing Coverage:

- Functional Testing: 100% test coverage for SHA-1 algorithm

- Timing Verification: Static timing analysis compliance

- Power Analysis: Dynamic and static power characterization

- Design Rule Checking: Full compliance with fabrication rules

Actual Implementation Results:

- Successful Hardening: OpenLane successfully translated Verilog to standard cells

- Physical Layout: 40μm and 2μm scale hardened user project area

- Precheck Compliance: Passed all eFabless verification requirements

- MPW-7 Submission: Successfully submitted to eFabless Open MPW Shuttle program

- User Project Wrapper: Integrated power lines, management SoC, and I/O connections

Design Workflow Lead Achievements (My Contributions):

- Complete SHA-1 Implementation: Designed and implemented the full 160-bit SHA-1 hashing core in Verilog/VHDL

- End-to-End Design Flow: Managed the entire process from RTL design to GDSII fabrication files

- Verification Framework: Developed comprehensive testbenches ensuring 100% functional coverage

- Technical Documentation: Established standards that became the foundation for future ASIC projects

- Industry Integration: Coordinated with eFabless partners and managed the fabrication submission process

Project Management Metrics

Documentation Completeness:

- 9 Weekly Reports: Comprehensive progress tracking

- 6 Bi-Weekly Reports: Detailed technical summaries

- 2 Design Documents: Complete technical specifications

- 6 Lightning Talks: Professional presentations

- Final Deliverables: IRP presentation, poster, and documentation

Team Performance:

- Role Specialization: Clear division of responsibilities

- Communication: Regular stakeholder updates and coordination

- Quality Assurance: Rigorous testing and validation processes

- Knowledge Transfer: Comprehensive documentation for future teams

Timeline Adherence:

- Phase 1 Completion: All CPR E 491 deliverables on schedule

- Phase 2 Completion: All CPR E 492 deliverables on schedule

- Fabrication Submission: Successful eFabless shuttle submission

- Final Presentation: Professional IRP panel presentation

Educational Framework Impact

First-Time Implementation:

- Pioneering Framework: First undergraduate ASIC fabrication program

- Industry Integration: eFabless partnership for real fabrication

- Tool Chain: Professional-grade design and verification tools

- Documentation Standards: Comprehensive framework for future teams

Knowledge Transfer:

- Process Documentation: Step-by-step fabrication guide

- Best Practices: Lessons learned and recommendations

- Tool Tutorials: Design tool usage instructions

- Future Guidelines: Framework for subsequent projects

Academic Integration:

- Curriculum Enhancement: Bridged theory-practice gap in computer engineering

- Hands-On Learning: Real hardware fabrication experience

- Industry Standards: Professional-grade design methodologies

- Research Foundation: Framework for advanced ASIC research

Team Dynamics and Peer Assessment

Team Performance Evaluation:

- Midterm Peer Assessment: Comprehensive evaluation of individual contributions

- End-of-Semester Peer Assessment: Final team performance review

- Role Effectiveness: Assessment of specialized responsibilities

- Collaboration Quality: Team communication and coordination evaluation

Individual Contributions:

- Design Workflow Lead (My Role): RTL design leadership, complete SHA-1 implementation, design flow management from RTL to GDSII, verification framework development, and technical documentation standards

- Component Design Lead: Architecture design and system integration

- Testing Lead: Verification framework and quality assurance

- Team Organization Lead: Project management and stakeholder coordination

Professional Development:

- Industry Exposure: Direct interaction with eFabless partners

- Technical Skills: Advanced ASIC design and fabrication techniques

- Communication: Professional presentation and documentation skills

- Leadership: Project management and team coordination experience

Technical Specifications:

- Team Size: 4 Computer Engineering students

- Fabrication: eFabless Open MPW Shuttle program

- Application: Bitcoin mining with SHA-1 hashing

- Tools: Verilog/VHDL, ModelSim, Cadence, Vivado

- Deliverables: 9 weekly reports, 6 bi-weekly reports, 2 design documents, 6 lightning talks

Comprehensive Documentation Archive:

- Project Selection: Senior Design group project selection documentation

- Team Formation: Team initiation agreement and contract documents

- Requirements: Engineering standards and constraints documentation

- Weekly Progress: 9 detailed weekly progress reports

- Bi-Weekly Summaries: 6 comprehensive bi-weekly technical reports

- Design Documents: Complete technical specifications for both semesters

- Peer Assessments: Midterm and end-of-semester team evaluations

- Final Presentations: IRP panel presentation and academic poster

- Educational Materials: Complete framework for future ASIC projects

Key Innovation: This project pioneered the first undergraduate ASIC fabrication framework at Iowa State University, establishing a complete pedagogical approach for digital ASIC design and fabrication. The team’s implementation of SHA-1 hashing for Bitcoin mining demonstrated practical application of ASIC technology while creating a replicable educational model for future computer engineering students.

Technical Contributions and Achievements

RTL Design Leadership:

- SHA-1 Implementation: Designed and implemented the complete SHA-1 hashing algorithm in Verilog/VHDL

- Cryptographic Architecture: Developed the 512-bit block processing unit and 160-bit hash generation system

- State Machine Design: Created control logic for hash computation flow and memory interface

- Performance Optimization: Implemented pipelined architecture for parallel hash operations

Design Flow Management:

- Synthesis Coordination: Led the entire logic synthesis and optimization process

- Place and Route: Managed physical design from floor planning to timing closure

- Verification Strategy: Developed comprehensive testbenches and functional verification

- Tool Integration: Coordinated ModelSim, synthesis tools, and verification frameworks

Documentation and Framework Development:

- Technical Specifications: Created detailed design documentation that became the standard for future teams

- Process Documentation: Established step-by-step fabrication guide and best practices

- Educational Materials: Developed tutorials and guidelines for subsequent ASIC fabrication projects

- Quality Assurance: Implemented rigorous testing and validation procedures

Cross-Disciplinary Integration:

- Physics Application: Applied physics principles to circuit design and optimization

- Programming Expertise: Utilized C, C++, Java, Python alongside VHDL and Verilog

- Workflow Optimization: Streamlined the entire design-to-fabrication process

- Industry Standards: Implemented professional-grade design methodologies

This project was completed as part of CPR E 491/492 (Senior Design) at Iowa State University.